这一篇blog是关于存储器设计那一章,据我的速成,发现这一章还是比较有条理的。

这一章主要是掌握位扩充和字节扩充,以及存储器地址译码电路的设计。实际上,这两点在计组里已经简要的涉及了,这里只是再作细化,同时最后将会引入在8086/8088里的情景,来考察一个较为真实的情景中的存储器扩充。

首先我们”revisit”一下所谓半导体存储器的存储容量,我们往往会用1MB,4K来称呼它们。严谨的表述是$N\times M$,这里$N$是字数,$M$是字长。我们可以认为“字”代表一个存储单元,所以$N$就是存储单元的数量;$M$就是每一个存储单元的长度。所以4KB(或许)就是4K×1B。

位扩展和字扩展

显然,单片存储器的容量很有限,所以我们需要将若干片芯片连接在一起,进行扩展。这就有两种方式,扩展$N$和扩展$M$,扩展$N$,实际上我们增加了存储单元(字)的数量,这称为“字扩展”;扩展$M$,我们增加了每个存储单元(字)的字长(位数),所以被称为“位扩展”。

从地址线和数据线的角度看,字扩展由于增多的是存储单元的数量,显然和负责存储单元寻址的地址线$A$挂钩;位扩展由于扩展了每一个单元的位数,显然和数据线$D$挂钩。

如果这时候你忽然意识到$AD_x$,或者什么“分时复用”之类的,先暂时忘掉8086,以下的讨论会在一个看起来不知从哪里来的,但又很符合计组当时学的的理想模型中建立,最后我再说这个”理想模型”是哪里来的。

以及还需要记住三种芯片的容量,如果考试出大题或许不会给:

| 芯片 | 容量 |

|---|---|

| SRAM Intel 6264 | 8K×8 |

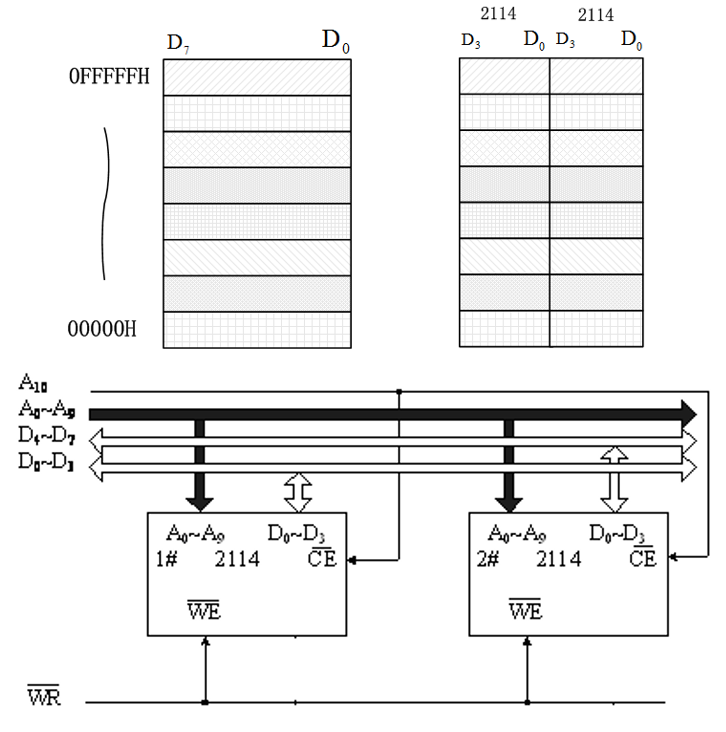

| SRAM Intel 2114 | 1K×4 |

| EPROM Intel 2764 | 8K×8 |

位扩展是简单的,只需数据线对应连接,这其实相当于芯片的并联。

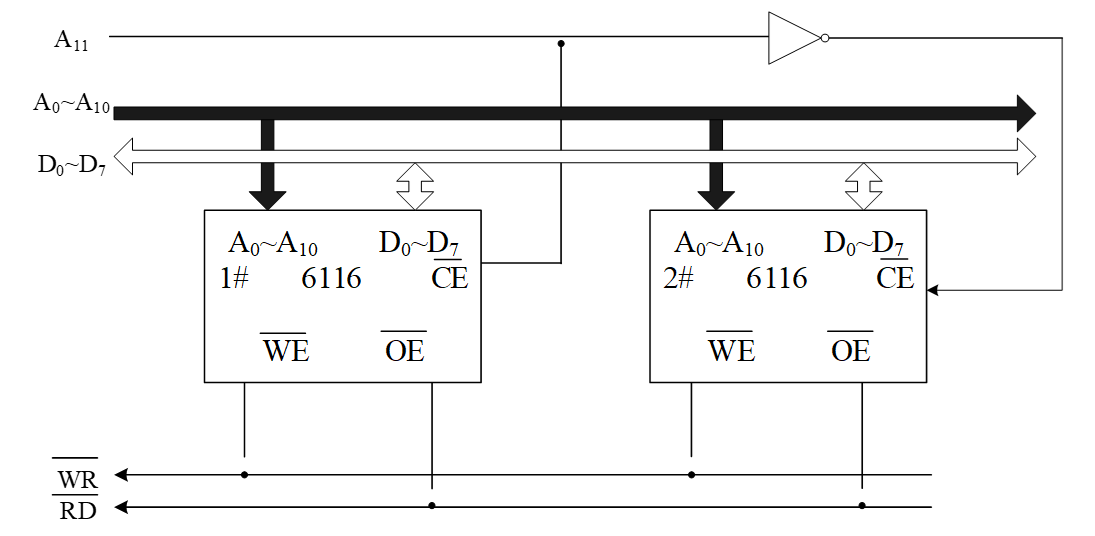

字扩展就稍微复杂一些了,此时依靠片选信号来决定启动哪块芯片,同时这种操作也使每个芯片占据不同的地址范围。

片选信号一般都是高位地址,比如这里的$A_{11}$,因为这样可以直接划分地址范围。那么在更复杂的情况下,片选信号的产生就不像上图中只用一个非门就解决了,可以采用组合逻辑电路和译码器。下面我们进行介绍:

首先我们要明确两个原则:①一次只能有一片芯片被激活,如果不这样,数据线就会发生竞争。②不一定所有的地址“都要有用”,比如对于一般的20条地址线,寻址空间是$2^{20}=1\mathrm{MB}$,并不是这整个$1\mathrm{MB}$都会用到,例如对于有些应用,只需256KB就够了,而多出来的地址本身就是冗余的。

全地址译码

顾名思义,这种方式需要用到所有的地址线,例如:

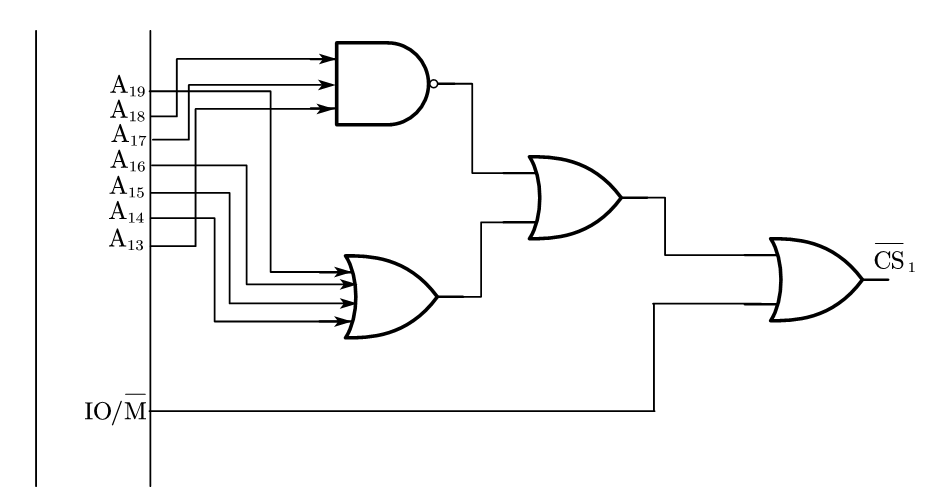

使用SRAM Intel 6264扩充设计8KB的片选信号电路,使用全地址译码方式。分配给该芯片的起始地址为62000H~63FFFH。

Intel 6264本身就是8K×8,所以只需一片。此时20位地址线需要全部参加译码,62000H~63FFFH写成二进制是0110 0010 0000 0000 0000B~0110 0011 1111 1111 1111B,所以我们发现前面的0110 001是固定的,一位一位读下来,其实就要求$A_{18},A_{17},A_{13}$全是1,$A_{19},A_{16},A_{15},A_{14}$全是0。所以译码电路即:(注意片选信号低电平有效)

这样可以保证,62000H~63FFFH与该芯片一一对应,但是组合逻辑电路就比较繁琐了。如果此时再加一个芯片,就需要填更多的逻辑元件。

部分地址译码

我们可以不用所有的地址线,只用一部分。仍然是一块6264,如果规定它的范围是0000 0000 0000 0000 0000B~0000 0001 1111 1111 1111B(00000H~01FFFH),按照全地址译码,这要求$A_{13}\sim A_{19}$全是0,如果我们不使用$A_{19}$,让最高位可以是任意的,那么相当于1000 0000 0000 0000 0000B~1000 0001 1111 1111 1111B(80000H~81FFFH)这一段空间,也被这一块芯片占用了。这称之为“重叠空间”。

不难看出,重叠空间数等于$2^n$,这可以简化译码电路,但付出了更多的可用空间,需要给一块芯片分配更多的地址范围。当然,并不是所有时候都需要用满1MB。到底不使用哪些高位地址,依照题目要求而定,例如:

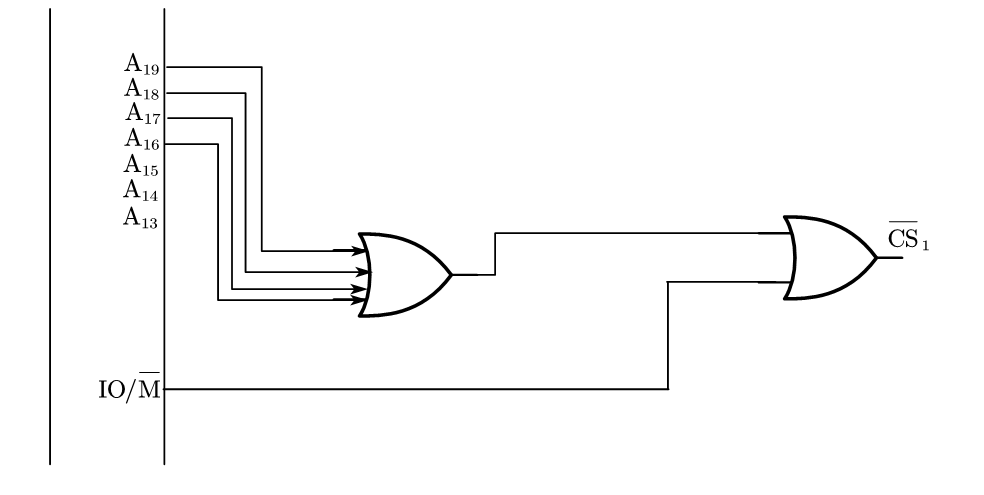

使用SRAM Intel 6264扩充设计8KB的片选信号电路,使用部分地址译码方式。分配给该芯片的范围为00000H~0FFFFH。

6264的字数是8K,即$2^{13}$,题目给出的地址范围是连续的,共$2^{16}$,这说明一块6264占了$2^{16-13}$即8块重叠区,所以3条高位地址线不参与译码。这3条显然是从$A_{13}$开始由低到高的三位,否则分配给芯片的范围就会是相互分离的区域,译码电路即为:

可以看出,译码电路简洁了很多。

线选译码

这种方式更为简单,无需多余的逻辑电路,直接将空出来的高位地址线和芯片的使能端相连,例如$A_{13}$直接连一个6264,$A_{14}$直接连另一个……优点是不需要再加逻辑电路,缺点就是地址空间显然存在大量重复区域。

从这里可以看出,部分译码是全译码和线选择码的混合。

译码器译码

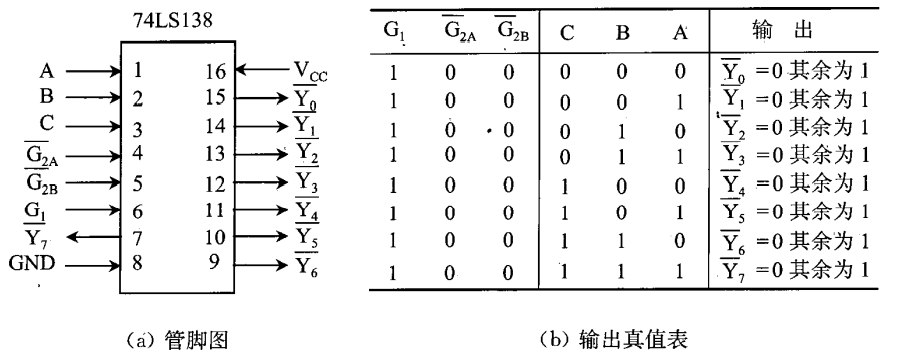

使用封装好的专用译码器,如74LS138,可以更方便的设计片选电路。用译码器,可以方便的实现上述的各种译码方式,我们先给出74LS138的管脚图和真值表:

注意到$A,B,C$二进制转十进制后恰好就是激活的$Y$端口,至于Y端口指向哪些地址,就要看输入了。所以一种简洁可行的译码方式,就是少许的组合逻辑电路+74LS138。

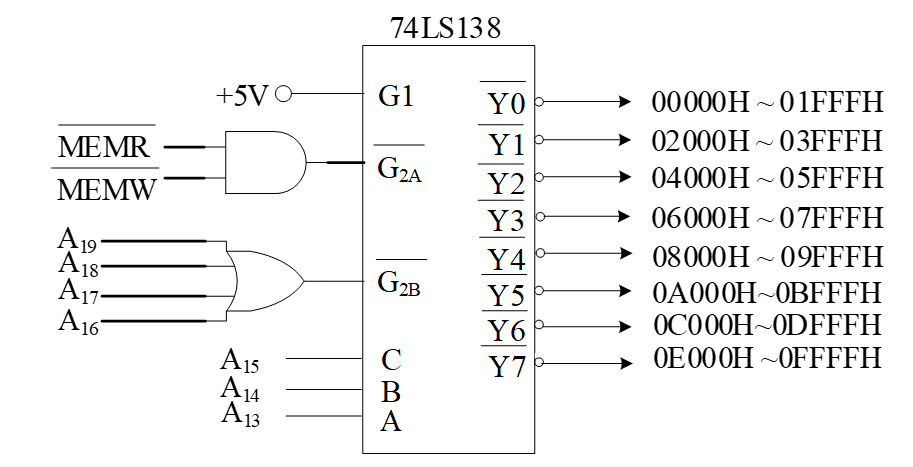

例如,用8片6264构成一个64KB的存储器,地址分配在00000H~0FFFFH,地址译码采取全译码方式,使用74LS138的话,只需让$A_{16}\sim A_{19}$控制74LS138的一个使能端即可,整体的连接即:

原理即:$A_{16}\sim A_{19}$使用一个或门控制低电平有效的使能端,这就使得$A_{16}\sim A_{19}$全为零。64KB为$2^{16}$,6264为$2^{13}$,剩下三个$A_{13},A_{14},A_{15}$直接接进来,很自然的可以分别计算出存储空间,例如当$A_{15}A_{14}A_{13}$分别为011时,取值范围就是0000 011x xxxx xxxx xxxx,全0是06000H,全1是07FFFH,与上图的$\overline{Y_3}$是一致的。

使用时可以非常灵活,例如如果想用6264扩充一个8KB的存储器,起始地址从04000H开始,我们发现其实正好对应着上图的$\overline{Y_2}$,此时也可以直接接这个电路,然后只引$\overline{Y_2}$,比构造门电路要简洁一些。

8086&8088

在上面的论述中我们一直使用的是一个地址线$A_0\sim A_{19}$,数据线$D_0 \sim D_7$的模型。实际上,8088CPU的地址总线正好就是20条,数据总线正好就是8条。而8086就不是了,所以如果考试考存储器扩展,均默认在8088最小系统下扩展设计。我们前面介绍的,正是对于一般的8位微机系统的存储器接口设计方法。

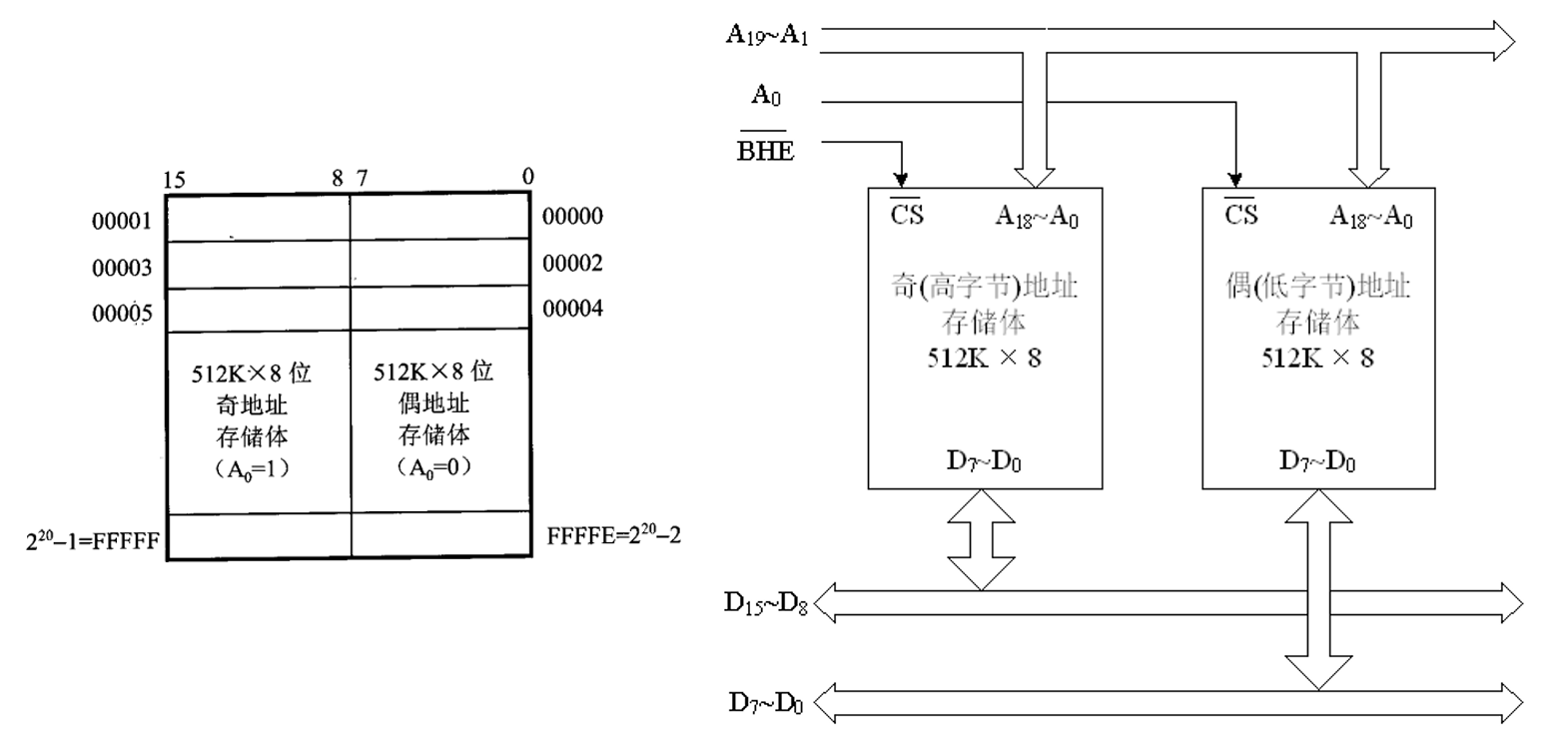

8086的不同之处在于,它是16位数据线的。在8086系统中,1MB的存储空间被分为两个存储体,偶地址存储体和奇地址存储体,各自为512KB,如下图所示:

图里的$\overline{\mathrm{BHE}}$和$A_0$的搭配,在总线那章就已经出现了,只不过在当时为了认识的方便,我当时写的是:“高8位/低8位”。现在根据上面的图,我们知道了$\overline{\mathrm{BHE}}$控制奇地址存储体,$A_0$控制偶地址。我们现在更正一下:

| $\overline{\mathrm{BHE}}$ | $\mathrm{AD}_0$ | 数据总线情况 |

|---|---|---|

| 0 | 0 | 从偶地址传送一个字 |

| 0 | 1 | 从奇地址传送一个字节 |

| 1 | 0 | 从偶地址传送一个字节 |

| 1 | 1 | 无效 |

这同样要将记忆拉回初学汇编语言时,那时候因为是从8086学习,所以都会用DoubleByte,往往会画成一个长条网格,在学习到例如[SI]等操作时,我们会非常自然的认为,[SI]一次次INC,然后遍历数据,进行读写。然而因为奇偶地址的设计,导致事实并不是这样的。

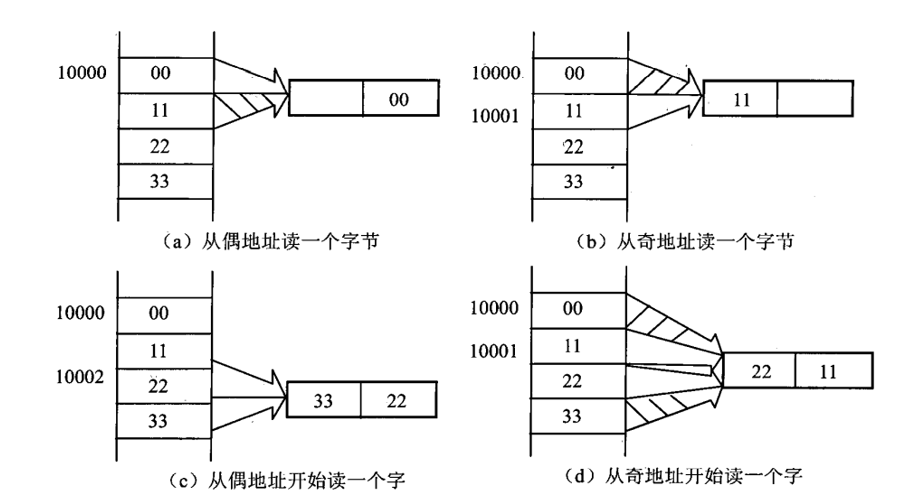

谜题的答案来自上面给出的这些设定:当我们想取一个字时,我们会同时选通两个存储体,此时$A_0=0$,这就导致无论每次给的$A_{19}\sim A_1$是什么,这个地址总会是偶数,且偶数正好也是低地址。所以如果要读取一个字,且这个字的低位字节是偶地址,那么只需$\overline{\mathrm{BHE}}=0,A_0=0$,访问一次即可。如果这个字的低位字节是奇地址,那么就需要访问两次,第一次取奇地址数据,第二次取偶地址上的数据,即先$\overline{\mathrm{BHE}}=0,A_0=1$,然后再$\overline{\mathrm{BHE}}=1,A_0=0$。所以为了加快运行速度,应主意从存储器偶地址开始存放字,这种方式也被称为“对准存放”。

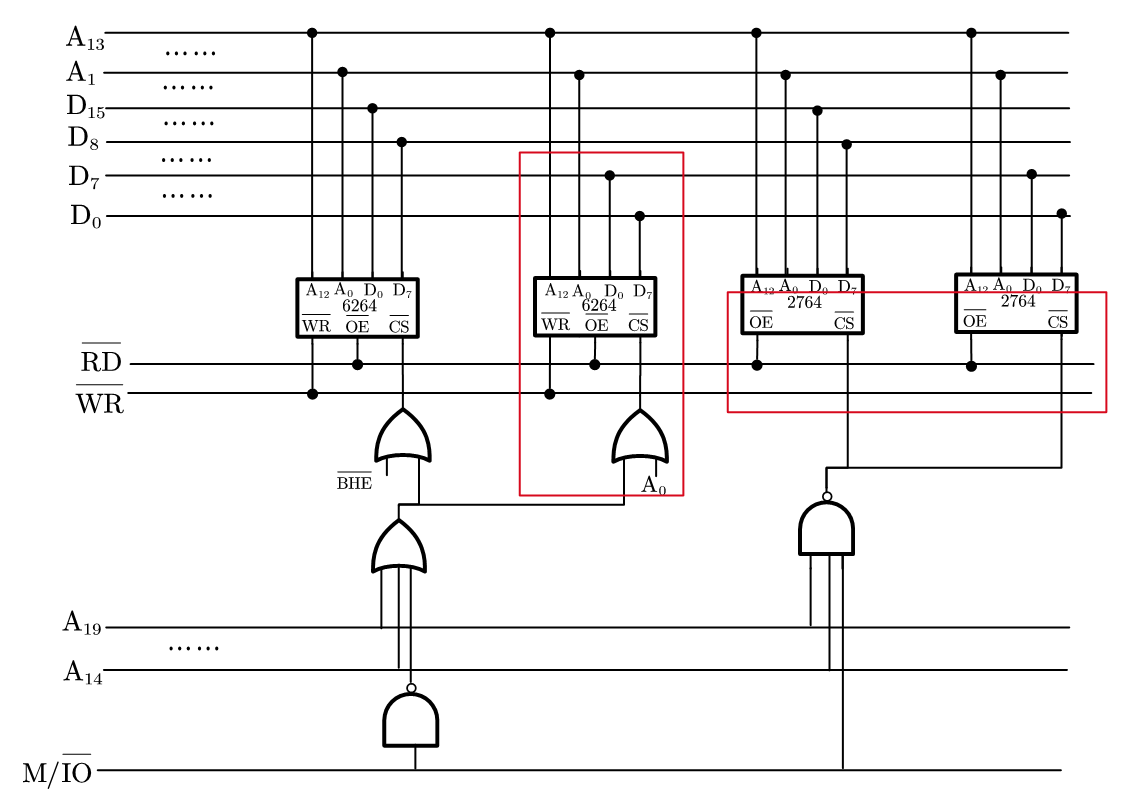

现在我们考虑一个8086时的存储器的连接:扩充设计16KB的EPROM和SRAM电路,SRAM选用Intel 6264,地址从00000H开始,EPROM芯片选用Intel 2764,地址从FC000H开始,作出连接图:

先读地址,16KB是$2^{14}$,且8086有16位,这两种RAM和ROM芯片都是8KB,所以不需字扩展,只需位扩展即可,各自用2块芯片。所以地址可直接被高六位控制,SRAM从00000H开始,那高六位显然都是0;EPROM从FC000H开始,即1111 1100 0000 0000 0000B,所以高六位全是1,那这就好办了。

以及从图中就可以看出,我们接8086的存储器设计的图时,不需要考虑时分复用,就画成地址线和数据线就好。

注意两个细节,$A_0$所连的一定要是偶存储体,以及ROM芯片是没有$\mathrm{WR}$的,因为16位时,ROM只需读出,无需写入,所以就导致可以直接用16位处理,不需分奇偶。此时片选电路也比较简单,不需要译码器。

更多的例题可以参照课本,这里就不再给出了(主要是画图太累了)。

End

这一章基本就是掌握扩展方法和接电路的方法,大部分情况下都是连8088,当然8086的连法也要掌握,以及记住那三种常见的芯片,这一章就没啥问题啦。