两周没听课,微机原理又讲到后半本书了。感觉没有前半本书直接和有逻辑性,有点杂乱。这一篇主要捋一下关于西电教材-第五章-总线的知识点。

我觉得,越学到后面,就像,吃螃蟹一样。必须,用一种够巧妙的方式来理解,才能逻辑连贯。不然会撞上不可逾越的知识壁垒……比如,这一篇里会涉及到一个元件“三态门”,如果真探究到底,那么就会遇到:

显然……这对于时间有限,而且有考核要求的我来说,是不可取的。所以下文不会讨论那些十分高深的内容,只是有条理的总结考试内容。

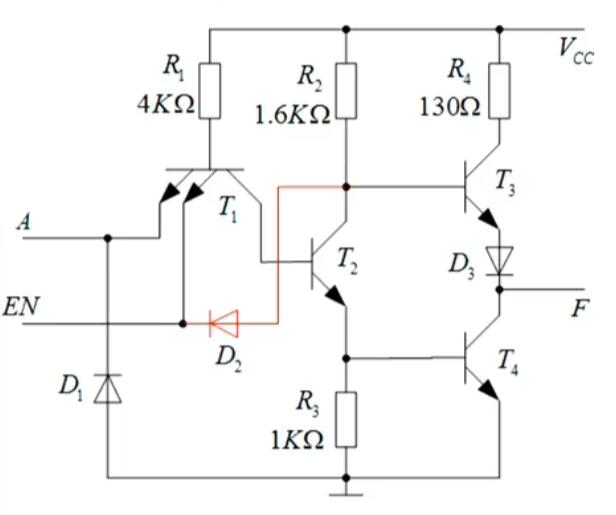

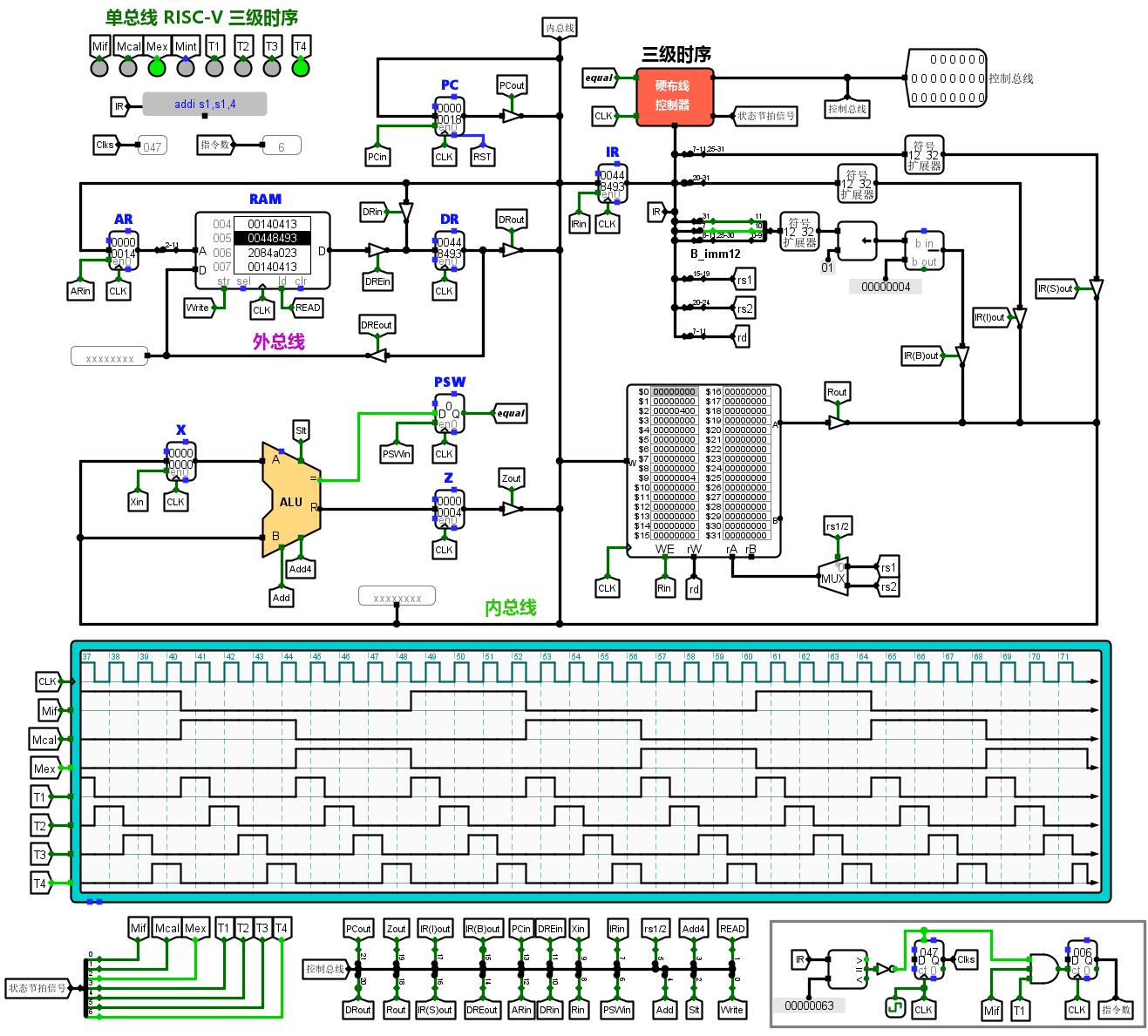

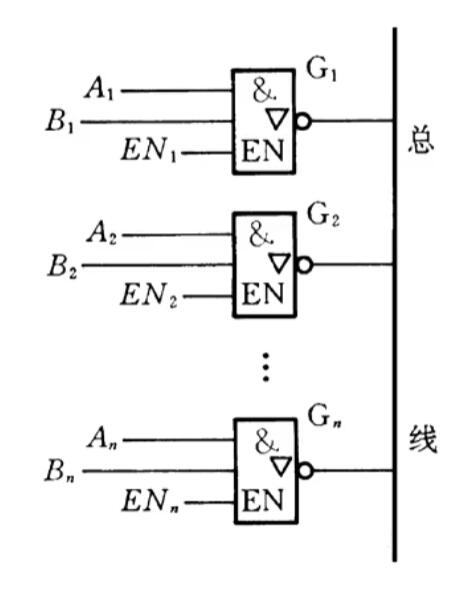

我继续召唤出这个玩具CPU,我当时在学CPU的那篇里,提到了两点:①这些“线”有规律的亮起,来一步步完成指令。②同一时钟周期内“线”上只能有一组数据。实际上这很好的刻画了,总线的特点。第一点,再仔细观察,其实是靠一种叫“三态门”的元件实现的。如果这个寄存器只需要out,那么可能三态门是单向的,例如上图中的Zout。但是有时候是需要双向的,即能读又能写,比如数据寄存器,就有一个DRin和一个DRout。第二点,由于总线上只能走一组数据,是一种竞争性资源。所以像地址一样的数据,可能需要寄存,这也就是计组中的取指令:M[PC]→IR,的用处,它将数据暂存到地址寄存器,等要用到的时候,再激活IRout的使能端,地址就又出来了。

但是8086毕竟更复杂一些,有些地方更加复杂,而且写法不太一样,但我们仍然能从中看出一些类似的性质。:

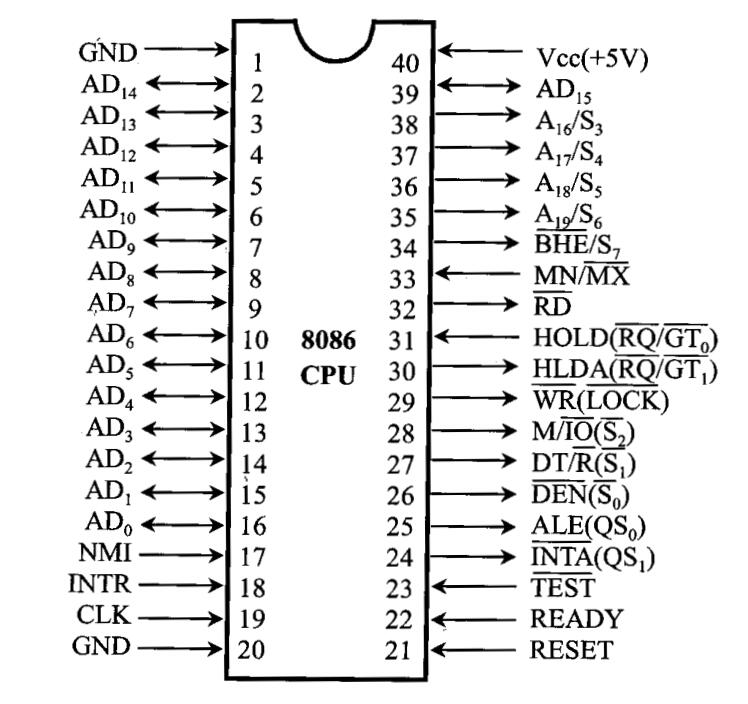

首先,8086CPU肯定不像上面那个玩具一样,它是封装好的,对外露出40根引脚。我们一种一种的看:

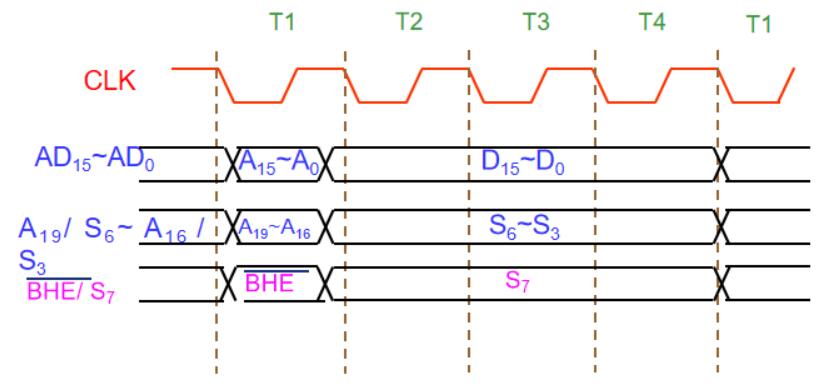

1.$\mathrm{AD_{15}}\sim\mathrm{AD_{0}}$

它叫Address Data Bus,这里的Bus指的就是总线。它们一共有16条,有三种状态,即“三态”。这种策略也被称为分时复用。

在总线周期$T_1$状态,用于输出储存器或者IO端口的地址,在$T_2$到$T_4$状态,用来传送数据,此时是可以双向输入/输出的。这里的“三态”,“双向输入/输出”,如果看上面的toy model,这比较好理解;但如果看教材上甩的一堆74LS244什么的,会非常困惑。这里我找到了一个折中的例子:

如图左侧的情形,$G_1,G_2,G_3$三个外设都想往总线上输入数据,如果没有三态门,就需要接逻辑门做控制,比如一个纯组合逻辑电路。有了三态门以后,直接相连,使用使能端来起到开关。只要使能信号分配好了,电路就能正常工作。同一时刻只能有一个外设在写入,其余都应关闭。而且高阻态这个状态,不同于低电位。对于总线来说,如果外设处于高阻态,那其实相当于不存在。但如果是低电位,可能出现电压不稳等情况,这个不是很清楚,从略了。

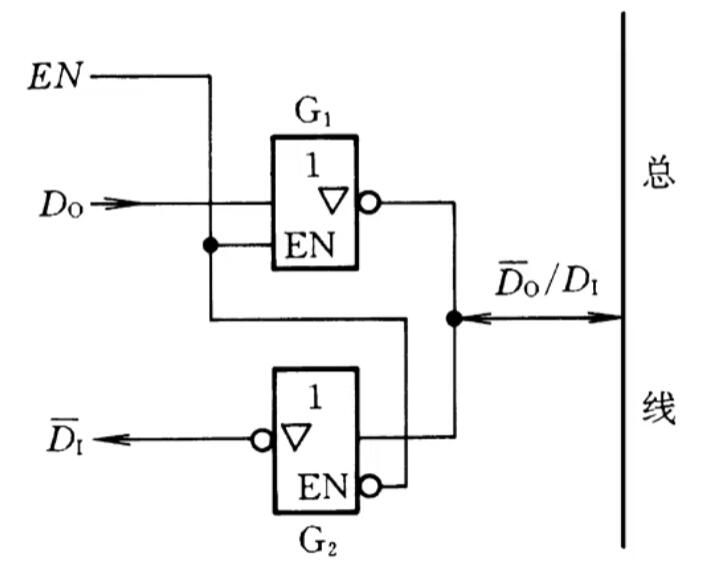

数据的双向传输也是通过上图所示的装置实现的,这样只需通过一个使能端,就可以控制数据是从外设写入总线,还是从总线写入外设。

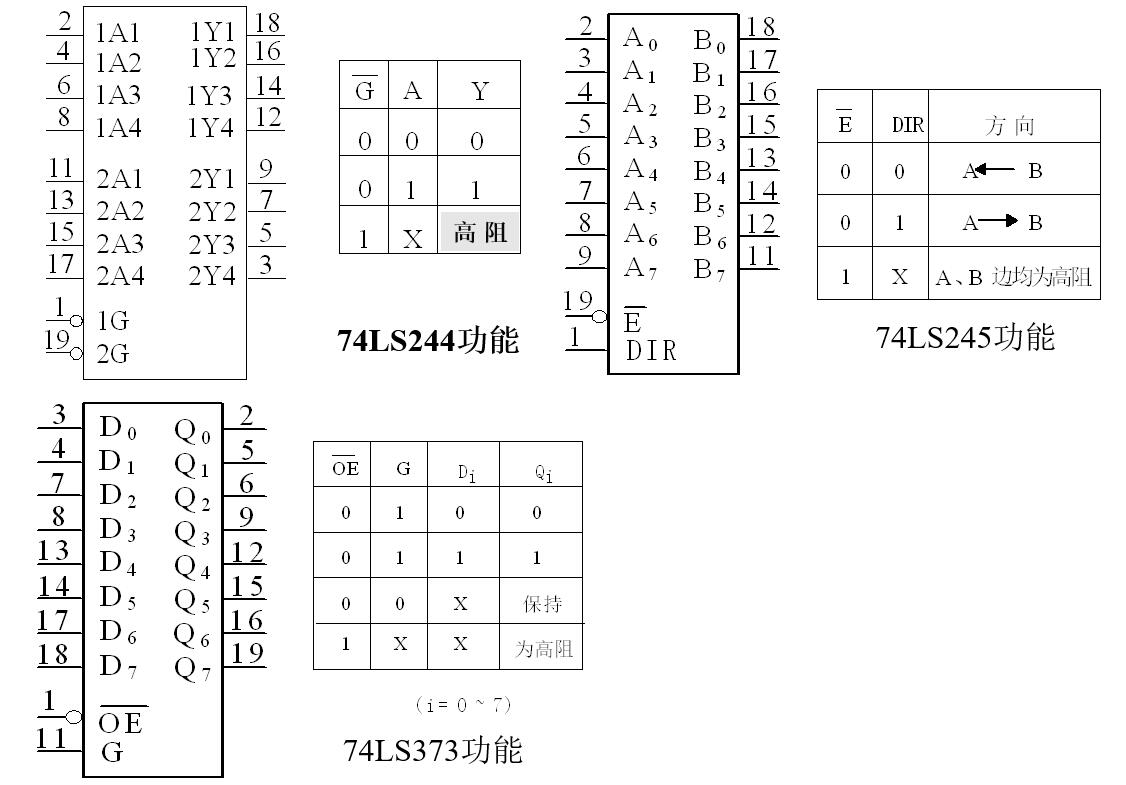

现在我们再来看,基于上述原理,封装的三种常用的芯片,74LS244,74LS245,74LS373。

简单来说,74LS244和74LS245分别是单向和双向的信号缓冲器。由三态门的特性,它们可以用来防止竞争。74LS373是一个锁存器,它实现了寄存功能。所以前两者常用来作驱动芯片,后者常用来作地址总线锁存器。

2.$\mathrm{A}_{19}/\mathrm{S}_{6}\sim \mathrm{A}_{16}/\mathrm{S}_{3}$

这里A指代Address,S是Status。同样,分时复用。在$T_1$状态,与16个$AD$一起,组成20位物理地址。当$T_2$到$T_4$状态,用于输出状态信息,$S_6$为0,说明此时8086连接在总线上,$S_5$表示中断,$S_3,S_4$用来编码此时所使用的段寄存器名:

| $S_4$ | $S_3$ | 段寄存器 |

|---|---|---|

| 0 | 0 | ES |

| 0 | 1 | SS |

| 1 | 0 | CS(I/O, INT) |

| 1 | 1 | DS |

3.其余引脚

$\overline{\mathrm{RD}}$即Read,三态输出,表明此时CPU正在读。

$\overline{\mathrm{WR}}$即Write,三态输出,表明此时CPU正在写。

$\mathrm{M}/\overline{\mathrm{IO}}$即memory/input and output,三态输出,表示是访问存储器还是IO端口。

$\mathrm{READY}$即ready,高电平有效,由外部输入,表示CPU所访问的存储器或IO端口已准备好传输数据,当READY无效时,CPU会插入一个或者多个等待周期$T_w$,直到READY就位。

$\mathrm{INTR},\overline{\mathrm{INTA}},\mathrm{NMI}$是三个关于中断的控制信号,估计下下章会涉及。

$\overline{\mathrm{TEST}}$是一个测试信号,由外部输入,当CPU执行WAIT指令完成处理器与外部硬件的同步时,WAIT指令会每隔5个时钟周期对TEST进行一次测试,如果测试为高电平,则继续WAIT。反之执行下一条指令。

$\mathrm{RESET}$也是由外部输入的复位信号,类似长按电脑5秒强制关机。$\mathrm{RESET}$至少要保持4个时钟周期。CPU接收到这信号后,停止进行操作,将各寄存器清零。而将CS设置为FFFFH。当$\mathrm{RESET}$信号结束后,CPU从FFFF0H开始执行程序(16×CS+IP 代码段地址)

$\mathrm{MN}/\overline{\mathrm{MX}}$即Minimum/Maximum,指的是CPU的工作模式。低电平时是MN,最小工作模式。高电平时是MX,是最大工作模式。这两种工作模式我们在后面介绍。

$\mathrm{CLK}$即时钟信号,不需多说。

$\mathrm{HOLD},\mathrm{HLDA}$是两个关于总线与CPU的信号,我们以一个例子来理解它们:

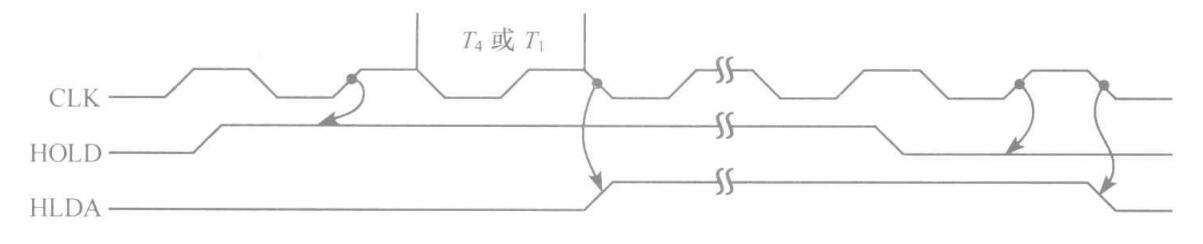

直接存储器访问(direct memory access)DMA将数据从一个地址空间复制到另一个地址空间,提供外设和存储器之间或者存储器和存储器之间的高速数据传输。这个技术的关键在于跳过CPU借助总线。当DMA控制器需要占用总线时,会向CPU发出总线请求HOLD(Hold Request),CPU收到有效的HOLD信号后,如果允许让出总线,会在当前总线周期完成时,发出HLDA(Hold Acknowledge)信号,同时使地址总线,数据总线,控制总线处于高阻态,表示让出总线。在下一个时钟周期,总线请求部件收到HLDA信号,获得总线控制权。在这期间HOLD与HLDA都处于高电平,直到总线请求部件完成对总线的栈用,使HOLD变为低电平,撤销总线请求,CPU收到后,HLDA变为低电平,CPU恢复对总线的控制。

下面这四个引脚往往会在一起出现:

$\mathrm{ALE}$是Address Lunch Enable,是地址锁存允许信号。

$\mathrm{DT}/\overline{\mathrm{R}}$是数据发送/接收控制信号,用来控制读写方向。

$\overline{\mathrm{DEN}}$是数据允许信号。

$\overline{\mathrm{BHE}}$是总线高位有效信号,它与$\mathrm{AD}_0$一起编码,给出总线的使用情况。我们后面会写到。

最小工作模式

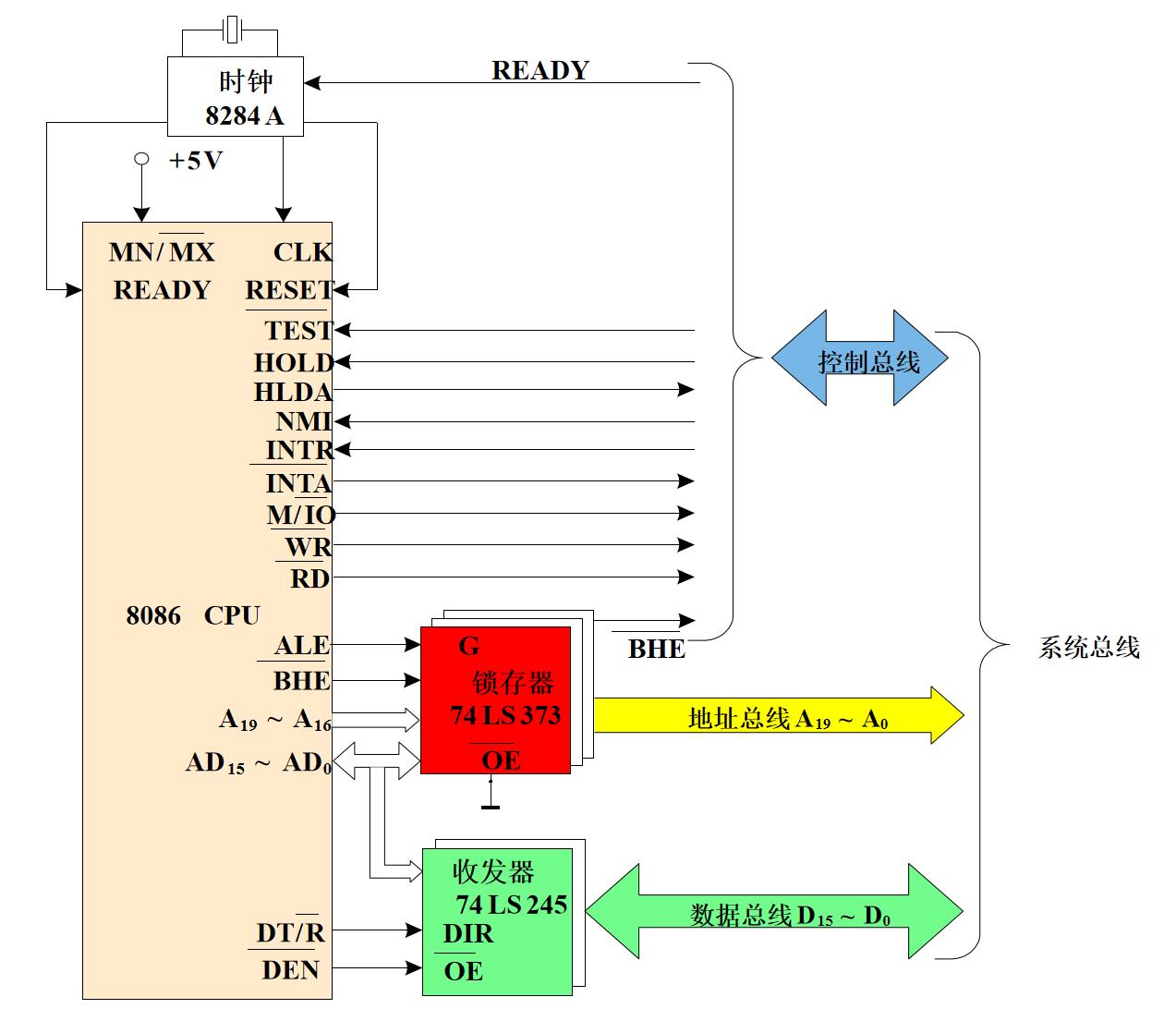

最小工作模式中,系统只有一个微处理器,系统所需的所有控制信号全部由8086直接产生。

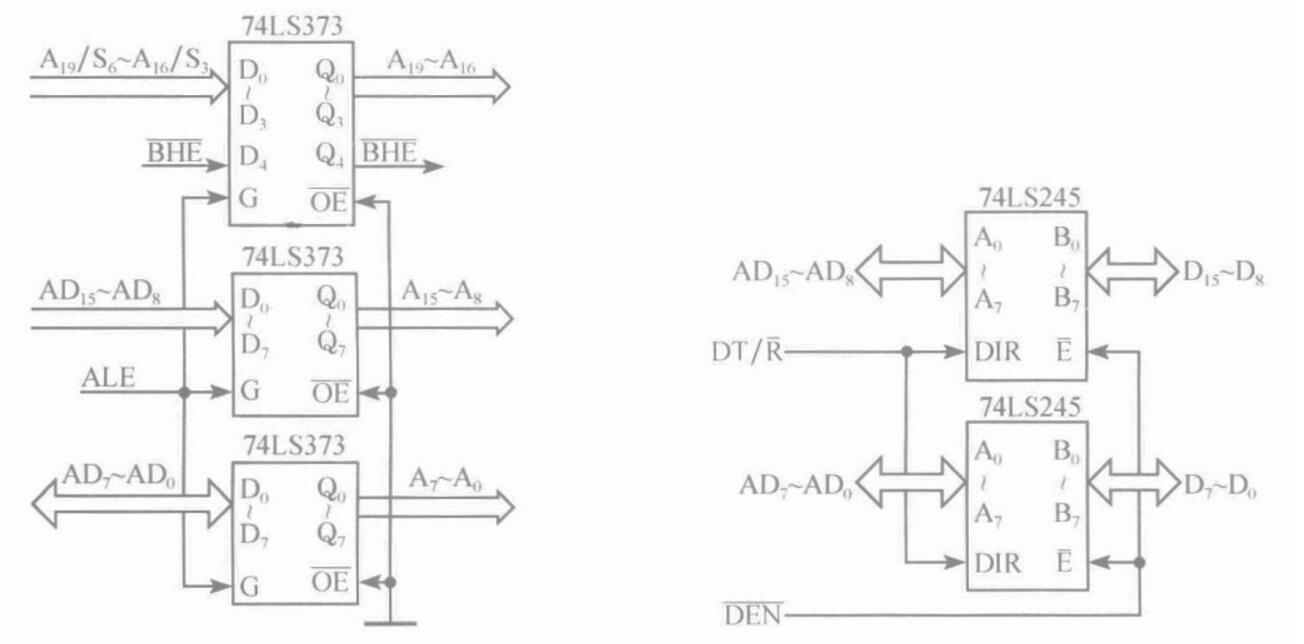

由于在8086中,依照之前的叙述,数据线和地址线是复用的。所以地址锁存器是必要的。在对存储器进行访问时,要先将地址输出。此时复用的引脚是地址线,当利用地址锁存器保存这些地址后。这些引脚才是数据线,将数据读出或写入存储器。由于一片74LS373是8位的,所以图中画了三片。而数据总线共16位,所以两片就够用了。如下图所示:

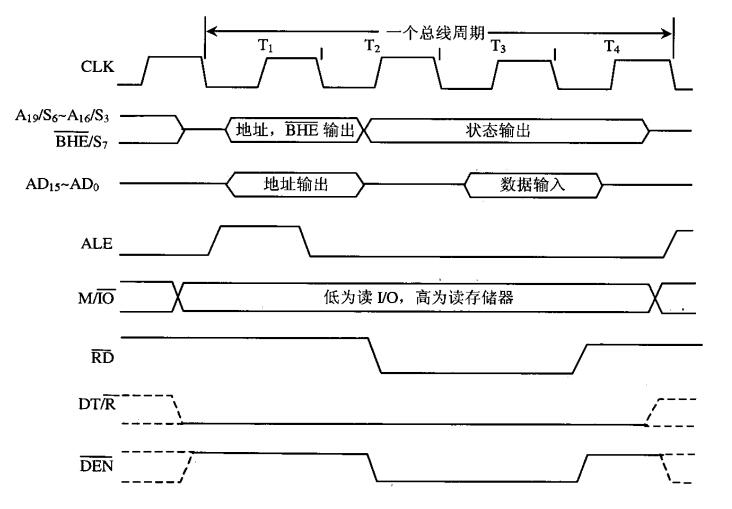

由于我们在上面给出了许多的引脚,不方便记忆,而且我们也很难知道这些引脚到底在CPU运行时是如何进行配合的。所以我们现在分别考察读/写总线周期时的时序:

T1状态:

$\mathrm{M}/\overline{\mathrm{IO}}$先指出CPU是从内存还是I/O端口读取数据,其有效电平一直保持到总线周期结束的$T_4$状态。然后,20位的地址信号输出,指出所要读取的地址。高4位从$\mathrm{A}_{19}/\mathrm{S}_{6}\sim \mathrm{A}_{16}/\mathrm{S}_{3}$送出,低16位从$\mathrm{AD_{15}}\sim\mathrm{AD_{0}}$送出。与此同时,总线高位有效信号$\overline{\mathrm{BHE}}$也被送到总线上。

之后,$\mathrm{ALE}$输出,使得地址锁存器将地址锁存。送到总线上的$\overline{\mathrm{BHE}}$与$\mathrm{AD}_0$,按下表给出下面数据总线的有效情况:

| $\overline{\mathrm{BHE}}$ | $\mathrm{AD}_0$ | 数据总线情况 |

|---|---|---|

| 0 | 0 | 16位数据总线进行字节传送 |

| 0 | 1 | 高8位进行字节传送 |

| 1 | 0 | 低8位进行字节传送 |

| 1 | 1 | 无效 |

同时,若系统中接有收发器如74LS245时,$\mathrm{DT}/\overline{\mathrm{R}}$会输出低电平,表示在读周期。

T2状态:

地址信号消失,$\mathrm{A}_{19}/\mathrm{S}_{6}\sim \mathrm{A}_{16}/\mathrm{S}_{3}$输出状态信息$S_6\sim S_3$,指出当前正在使用的段寄存器和中断允许情况。低地址线$\mathrm{AD_{15}}\sim\mathrm{AD_{0}}$进入高阻状态,为读取数据做准备。

此时$\overline{\mathrm{RD}}$信号有效,送到储存器或I/O端口,启动被选存储器或I/O端口。

同时,如果系统中接有收发器,$\overline{\mathrm{DEN}}$会有效,作为选通信号,使得收发器通过数据。

T3状态:

当被选的存储器或I/O端口在$T_3$周期来得及读出数据并送到数据总线上时,$\mathrm{READY}$信号会被置为有效。当$T_3$周期里的上升沿得知$\mathrm{READY}$有效,会在$\overline{\mathrm{DEN}}$和$\mathrm{DT}/\overline{\mathrm{R}}$的控制下,将数据总线上的16位或8位数据,经数据收发器缓冲后向CPU输入,同时$S_4S_3$会给出访问哪个段寄存器,如果是CS,那表示读取的是指令;CPU将它送入指令队列等待执行,否则读取的是数据,送入ALU。

如果在$T_3$周期里没来得及读出数据,那么会插入等待周期$T_w$,直到$\mathrm{READY}$有效。

T4状态:

从数据总线上撤销数据,各控制信号和状态信号变为无效。

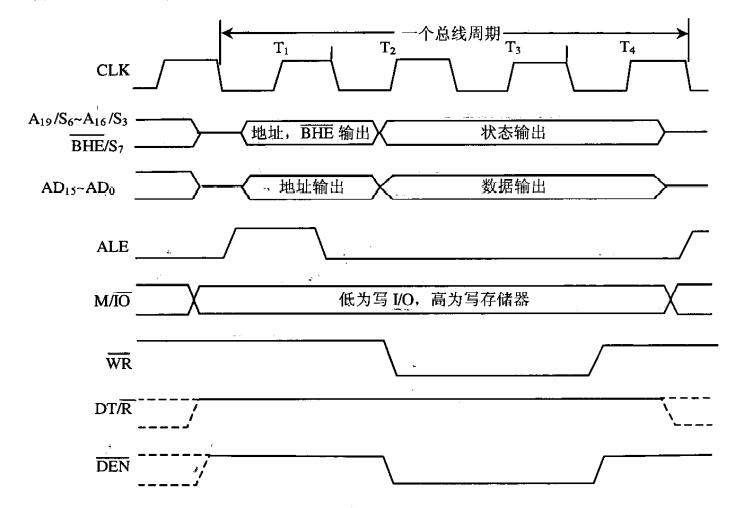

写总线时的时序与读时大同小异。只有几点不同:

$\mathrm{DT}/\overline{\mathrm{R}}$会表示为高电平,表示是写入。

$T_2$状态,地址信号输出后,CPU立即向$\mathrm{AD_{15}}\sim\mathrm{AD_{0}}$发出数据,使存储器或I/O一旦准备好即可取走数据。

用$\overline{\mathrm{WR}}$信号代替$\overline{\mathrm{RD}}$。

通过刚才的时序逻辑我们可以看出,在8086最小工作模式下,可以不用数据收发器,直接将$\mathrm{AD_{15}}\sim\mathrm{AD_{0}}$与存储器或I/O的数据线相连。

最大工作模式

最大工作模式指的是,系统有两个或两个以上的微处理器。这时系统所需的控制信号由总线控制器8288间接产生。首先,我们要明确最大模式下,8086CPU的24~31号引脚的定义:

| 引脚编号 | 最小模式 | 最大模式 |

|---|---|---|

| 24 | $\overline{\mathrm{INTA}}$ | $\mathrm{QS}_1$ |

| 25 | $\mathrm{ALE}$ | $\mathrm{QS}_0$ |

| 26 | $\overline{\mathrm{DEN}}$ | $\overline{\mathrm{S}_0}$ |

| 27 | $\mathrm{DT}/\overline{\mathrm{R}}$ | $\overline{\mathrm{S}_1}$ |

| 28 | $\mathrm{M}/\overline{\mathrm{IO}}$ | $\overline{\mathrm{S}_2}$ |

| 29 | $\overline{\mathrm{WR}}$ | $\overline{\mathrm{LOCK}}$ |

| 30 | $\mathrm{HLDA}$ | $\overline{\mathrm{RQ}}/\overline{\mathrm{GT}}_1$ |

| 31 | $\mathrm{HOLD}$ | $\overline{\mathrm{RQ}}/\overline{\mathrm{GT}}_0$ |

$\mathrm{QS}_0,\mathrm{QS}_1$是提供8086CPU内部指令队列状态的编码,这两个引脚的目的是让外部设备监视CPU内部的指令队列,可让协处理器8087进行指令的扩展处理,这里不作过多介绍。

$\overline{\mathrm{S}_0},\overline{\mathrm{S}_1},\overline{\mathrm{S}_2}$会输入总线控制器8288,8288对它们进行译码后代替CPU输出相应的控制信号,我们后面会再提到。

$\overline{\mathrm{LOCK}}$有效时,表示CPU不允许其他总线主控者(比如之前例子里的DMA系统,其他CPU)占用总线。

$\overline{\mathrm{RQ}}/\overline{\mathrm{GT}}_1,\overline{\mathrm{RQ}}/\overline{\mathrm{GT}}_0$这两个引脚类似HOLD和HLDA,用于不同处理器之间的连接控制。

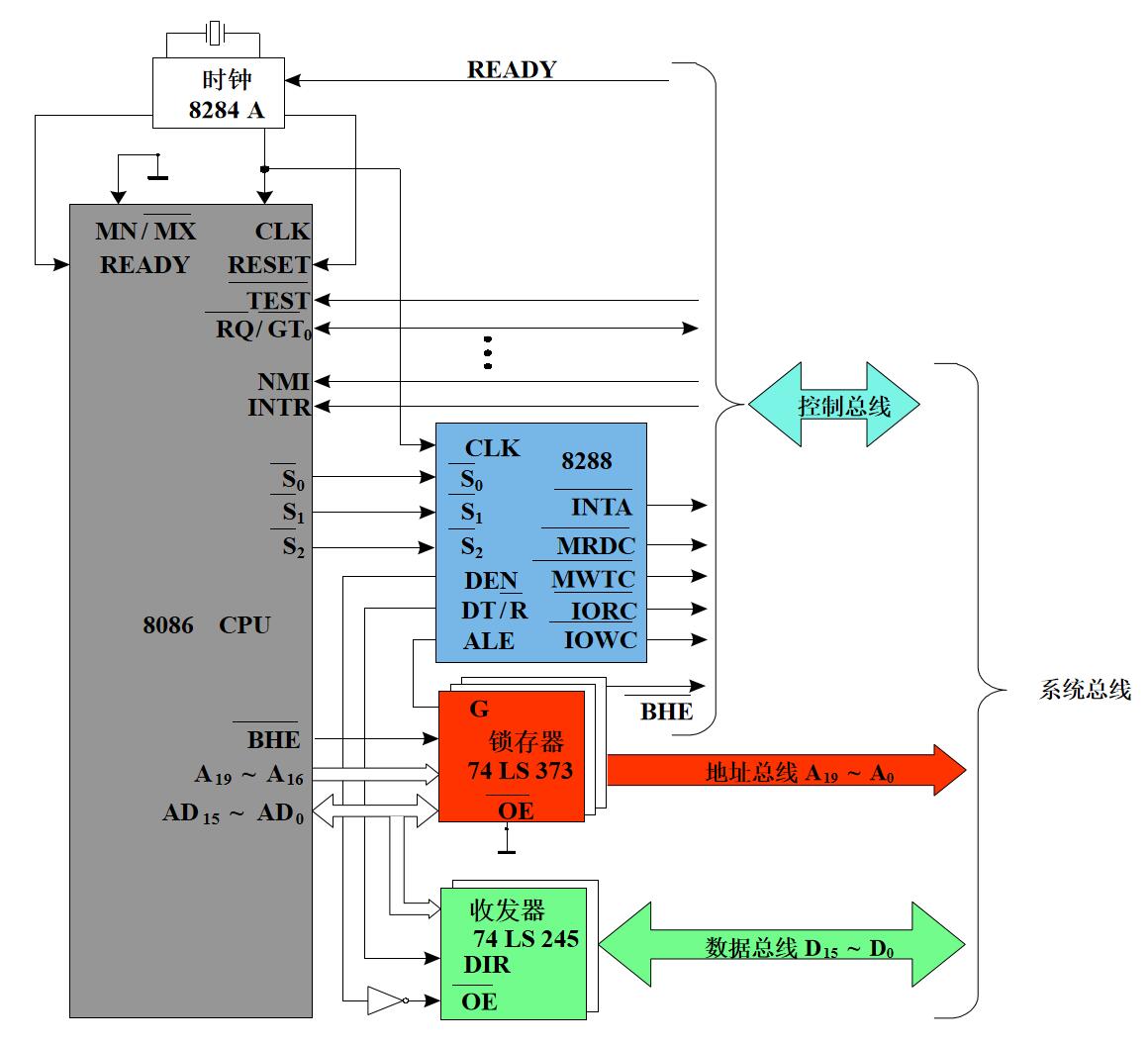

上图展示了8086最大方式下的总线结构,观察中间的总线控制器8288,它主要生成存储器和I/O端口的读写信号($\overline{\mathrm{MRDC}},\overline{\mathrm{MWTC}},\overline{\mathrm{IORC}},\overline{\mathrm{IOWC}}$)和$\mathrm{ALE}$,${\mathrm{DEN}}$,$\mathrm{DT}/\overline{\mathrm{R}}$。注意此时由8288生成的${\mathrm{DEN}}$极性与8086CPU单独发出的相反。

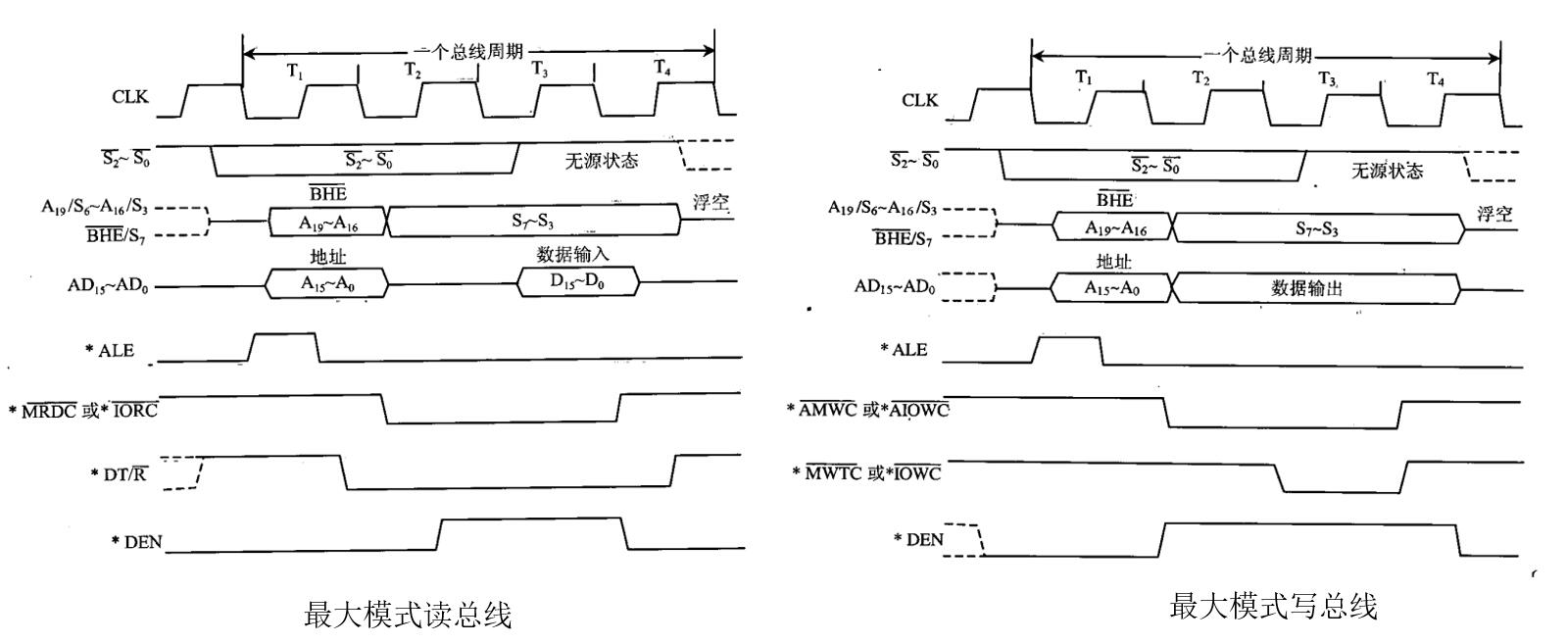

上图给出了最大模式下的读总线和写总线,我们可以观察它与最小模式的不同之处。

只要检测到$\overline{\mathrm{S}_0},\overline{\mathrm{S}_1},\overline{\mathrm{S}_2}$任何一个或者几个为低电平,则立即开始一个新的总线周期。

$\overline{\mathrm{MRDC}}$和$\overline{\mathrm{IORC}}$指出是读存储器还是I/O端口,代替了读信号$\overline{\mathrm{RD}}$,相当于最小模式中的$\mathrm{M}/\overline{\mathrm{IO}}$和$\overline{\mathrm{RD}}$。进入$T_3$状态后,$\overline{\mathrm{S}_0},\overline{\mathrm{S}_1},\overline{\mathrm{S}_2}$全部进入高电平,这种状态称为无源状态。一直维持到$T_4$,这意味着很快可以启动一个新的总线周期。

写总线时,也和最小模式一样,当地址输出后,CPU在$T_2$状态就把数据送到数据总线$\mathrm{AD_{15}}\sim\mathrm{AD_{0}}$。

8086与8088

在第五章的最后,教材介绍了8086与8088的差异。这里总结如下:

| CPU内部 | ||

|---|---|---|

| 差异 | 8086 | 8088 |

| 指令队列寄存器 | 6字节 | 4字节 |

| CPU外部 | ||

|---|---|---|

| 差异 | 8086 | 8088 |

| 数据总线 | 16条$\mathrm{D_{15}}\sim\mathrm{D_{0}}$ | 8条$\mathrm{D_{7}}\sim\mathrm{D_{0}}$ |

| $\mathrm{AD_{15}}\sim\mathrm{AD_{0}}$ | 分时复用 | 单一地址线 |

| 存储器/IO | $\mathrm{M}/\overline{\mathrm{IO}}$ | $\mathrm{IO}/\overline{\mathrm{M}}$ |

| 其它 | $\overline{\mathrm{BHE}}$ | $SS_0$ |

End

16号考模式识别,这预示着上强度的期末考试的来临。总线后是存储器设计,接口技术,中断系统和8295A,定时/计数器8253的应用设计。接口技术那一章比较水,但是另外这仨都不简单,争取每天解决一章吧。